# PROFIBUS DP Master-Stack für Altera FPGA

Sofort einsatzbereite Komplettlösung auf FPGA-Basis mit Protokoll-Stack und Fieldbus Controller

Der PROFIBUS DP Master für Altera FPGA umfasst alle benötigten Komponenten für die Realisierung eines vollumfassenden PROFIBUS DP Masters der Klasse 1 und 2 auf Basis der FPGA-Technologie. Auf den Einsatz eines zusätzlichen, spezifischen Fieldbus Controller-ASICs kann somit verzichtet werden.

### **Minimaler Entwicklungsaufwand**

- Kombination aller Komponenten für Implementierung eines PROFIBUS DP Masters der Klasse 1 oder 2 in Field Programmable Gate Array (FPGA)

- Bussteuerungslogik für PROFIBUS DP, als ladbarer IP Core realisiert

- PROFIBUS DP-Protokoll-Stack, sofort einsatzbereit für Ausführung auf Soft-Core-Prozessor des FPGAs

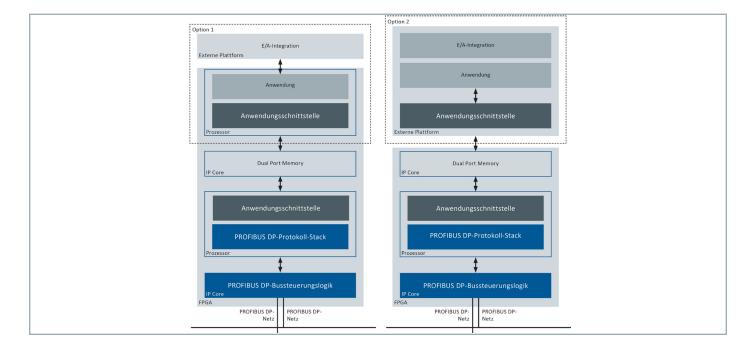

- Steuerungsanwendung wahlweise lauffähig auf einem zweiten Prozessor innerhalb des FPGAs oder auf externem Prozessor

- Unterstützung der PROFIBUS DP-Versionen DP (Austausch zyklischer Daten und Diagnosen mit Slaves), DP-V1 (azyklischer Datenaustausch und Alarmbehandlung) sowie DP-V2 (Uhrzeitsynchronisation und Zeitstempel)

### Flexibilität dank integriertem Fieldbus Controller

- Gesamte Bussteuerungslogik für Zugriff auf PROFIBUS DP-Netz

- Verarbeitung aller zeitkritischen Teile von PROFIBUS DP-Sicherungsschicht, Token-Verarbeitung und zyklischem Datenaustausch

- Keine Abhängigkeit von Fieldbus Controller-ASIC und dessen Hersteller

# Höhere Anlagenverfügbarkeit

- Unterstützung von Master-Redundanz mit stoßfreier Umschaltung vom primären PROFIBUS DP Master zum Backup-Master

- Optionale Linienredundanz-Funktionalität für Zugriff auf Feldgeräte über redundant ausgelegte Feldbuskabel

- Mögliche Nutzung für Prozessoptimierung

- Unterstützung der gezielten Umkonfiguration einzelner PROFIBUS Slaves im laufenden Betrieb

| Technische Daten                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                              |                                                             |  |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------------------------------------------------------------|--|

| Unterstützte Slave-Gerate                                 | ≤ 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                              |                                                             |  |

| Zyklische Ein- / Ausgangsdaten gesamt                     | ≤ 30.500 Bytes / ≤ 30.500 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                              |                                                             |  |

| Ein- / Ausgangsdaten pro Slave                            | ≤ 244 Bytes / ≤ 244 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |                                                             |  |

| Konfigurations- / Parameter- / Diagnosedaten pro Slave    | ≤ 244 Bytes / ≤ 244 Bytes / ≤ 244 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                              |                                              |                                                             |  |

| Protokolle                                                | PROFIBUS DP-V0, PROFIBUS DP-V1, PROFIBUS DP-V2                                                                                                                                                                                                                                                                                                                                                                                                                       |                                              |                                                             |  |

| PROFIBUS DP-V1-Funktionalität                             | <ul> <li>Alarme</li> <li>Erweiterte Diagnose</li> <li>Azyklisches Lesen/Schreiben (Klasse 1 und Klasse 2)</li> <li>Datenübertragung (Lastbereich)</li> </ul>                                                                                                                                                                                                                                                                                                         |                                              |                                                             |  |

| Weitere Funktionalität                                    | <ul> <li>Online-Änderungen (gezielte Umkonfiguration einzelner Slaves während des laufenden Betriebs)</li> <li>Historische Diagnoseinformation (Speicherung der Diagnosemeldungen bis zum Auslesen durch die Anwendung in einem FIFO-Speicher konfigurierbarer Größe)</li> <li>Optionale Synchronisation zwischen PROFIBUS DP-Abfragezyklus und Anwendung</li> <li>Vorverarbeitung der Eingangsdaten (Benachrichtigung der Anwendung bei Datenänderungen)</li> </ul> |                                              |                                                             |  |

| Optionale Funktionalität<br>(Bestandteil der Version pro) | <ul> <li>Master-Redundanz (stoßfreie Umschaltung des Masters, erfordert redundante Verbindung zwischen aktivem Master<br/>und Backup-Master)</li> <li>PROFIBUS DP-V2-Funktionalitat (Uhrzeitsynchronisation, Zeitstempel)</li> </ul>                                                                                                                                                                                                                                 |                                              |                                                             |  |

| Option (separat erhältlich)                               | Linienredundanz (Betrieb von 2 voneinander unabhängigen physikalischen Verbindungen)                                                                                                                                                                                                                                                                                                                                                                                 |                                              |                                                             |  |

| Systemanforderungen                                       | Speicher                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Code: 512 KB, RAM: 512                       | KB                                                          |  |

|                                                           | FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Altera Cyclone IV oder V (und SoC), Arria II |                                                             |  |

|                                                           | FPGA-Ressourcen                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Reiner IP Core                               | Typische Ausführung mit IP Core, Nios II, Memory Controller |  |

|                                                           | Logikelemente                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6 K                                          | 16 K                                                        |  |

|                                                           | Speicherblöcke (M10K)                                                                                                                                                                                                                                                                                                                                                                                                                                                | 13                                           | 65                                                          |  |

| Lizenzierung                                              | Einzel- oder Jahreslizenz                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                              |                                                             |  |

| Lieferumfang  |                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IP Core       | PROFIBUS DP-Bussteuerungslogik, FPGA-Design-Beispiel für Altera Cyclone V E Entwicklungskit (unter Nutzung des Cyclone V E FPGA - 5CEFA7F31I7N)                                                                                                                                                                                                                                  |

| Software      | <ul> <li>PROFIBUS DP Master-Stack, Binärformat</li> <li>PROFIBUS Access Kit (ermöglicht die Portierung der Protokoll-Zugriffsbibliothek in Bezug auf Hardware, Betriebssystem und Anwendungs-Software), Quellformat</li> <li>PROFIBUS-Beispielanwendung (vorkompiliert zur sofortigen Nutzung mit zweitem Soft-Core-Prozessor des FPGA-Design-Beispiels), Quellformat</li> </ul> |

| Dokumentation | Handbuch . PROFIBUS DP-Stack" und Benutzerhandbuch . PROFIBUS Master for Altera FPGA" elektronisches Format                                                                                                                                                                                                                                                                      |

#### Bestellnummern

| PROFIBUS DP Master, IP Core und Protokoll-Stack (DP-V0, DP-V1, ohne Master-Redundanz)          |                                                                                                                            |  |  |

|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| KXL-NN-016412                                                                                  | Entwicklungspaket (enthalt Software und Dokumentation, für beide Lizenzvarianten erforderlich)                             |  |  |

| ISL-YY-015310                                                                                  | Einzellizenz für 1 Master-Gerat (Security EEPROM, Verpackungseinheit: 250 Stück)                                           |  |  |

| LAA-NN-019310                                                                                  | Jährliche Produktlizenzgebühr (berechtigt zum Verkauf einer unbegrenzten Anzahl eines einzelnen Kundenprodukts für 1 Jahr) |  |  |

| LFA-NN-019340                                                                                  | Option: PROFIBUS DP-Linienredundanz für PROFIBUS DP Master IP Core (einmalige Gebühr für 1 Kundenprodukt)                  |  |  |

| PROFIBUS DP Master pro, IP Core und Protokoll-Stack (DP-V0, DP-V1, DP-V2 und Master-Redundanz) |                                                                                                                            |  |  |

| KXL-NN-016412                                                                                  | Entwicklungspaket (enthalt Software und Dokumentation, für beide Lizenzvarianten erforderlich)                             |  |  |

| ISL-YY-015311                                                                                  | Einzellizenz für 1 Master-Gerat (Security EEPROM, Verpackungseinheit: 250 Stuck)                                           |  |  |

| LAA-NN-019311                                                                                  | Jährliche Produktlizenzgebühr (berechtigt zum Verkauf einer unbegrenzten Anzahl eines einzelnen Kundenprodukts für 1 Jahr) |  |  |

| LEV-NNI-010340                                                                                 | Ontion: PROFIRITS DP. Liniagradundanz für PROFIRITS DP Macter ID Core (einmalige Gehühr für 1 Kundenprodukt)               |  |  |

## Ergänzende Produkte und Dienstleistungen

SIA-NN-018101 PROFIBUS DP-Integrations-Workshop

DDA-NN-006014 PROFIBUS Tester 5 (BC-700-PB)

TRA-PB-TECH PROFIBUS-Technologieschulung

Ihr lokaler Kontakt zu Softing:

Softing Industrial Automation GmbH Richard-Reitzner-Allee 6 85540 Haar / Deutschland Tel.: +49 89 456 56-340 Fax: +49 89 456 56-488 info.automation@softing.com http://industrial.softing.com

Softing Inc.

US-Zentrale

7209 Chapman Highway

Knoxville, TN 37920 / USA

Tel.: +1 865 251 52 52

Fax: +1 865 579 47 40

info@softing.us

http://www.softing.us

Softing Industrial Automation GmbH Äußere Sulzbacher Straße 159-161 90491 Nürnberg / Deutschland Tel.: +49 911 544 27-0 Fax: +49 911 544 27-27 info.automation@softing.com http://industrial.softing.com

Softing Inc.

US-Vertriebsbüro

29 Water Street, Suite 301

Newburyport, MA 01950 / USA

Tel.: +1 978 499 96 50

Fax: +1 978 499 96 54

info@softing.us

http://www.softing.us

Buxbaum Automation GmbH Thomas-Alva-Edison-Straße 1 7000 Eisenstadt / Österreich Tel.: +43 2682 704 560 Fax: +43 2682 205 77 00-5610 office@myautomation.at http://myautomation.at

Softing Italia Srl

Via Padre Massimiliano Kolbe, 6

20090 Cesano Boscone (MI) / Italien

Tel.: +39 02 450 51 71

Fax: +39 02 450 41 41

info@softingitalia.it

http://softingitalia.it